NEXT-GENERATION HARDWARE FOR COMMUNICATIONS & SENSORS

### **Editors' column**

Robert J. Runser & David J. Mountain

In this issue of The Next Wave (TNW), we conclude our series reviewing recent advances in NSA's hardware-oriented research. In the last issue, we focused almost exclusively on hardware that will enable the future of high-performance computers, as technologies driven by Moore's Law are sunsetting. In this issue, we review a broad range of novel architecture, hardware, and sensor research that will enable multiple applications including high-performance and secure computing, radio-frequency (RF) monitoring for secure facilities, localizing electric fields for device fault detection, and flexible antenna arrays for detecting multidirectional signals. We also include an article that reviews recent results using additive manufacturing techniques to enable electronics and sensors that adapt and conform to the application geometry and environmental constraints of the system. This issue features authors from multiple research organizations including NSA's research laboratories, the Pacific Northwest National Laboratory, the University of Cambridge, and the University of Maryland. We are extremely grateful for their contributions to this issue.

In the first article, "The road less traveled: Eliminating bottlenecks in high-performance computing networking," the authors provide a historical perspective on the development of different multi-node supercomputing topologies and compare three of the most promising architectures. In their analysis, the authors argue that non-traditional workloads, such as data analytics and artificial intelligence, will require topologies that dynamically remove bottlenecks and adapt to unpredictable workloads driven by new high-performance computing applications.

The next article introduces new extensions to instruction set architectures developed under the CHERI project to address one of the most difficult and long-standing challenges in cybersecurity: memory security. Developed over 10 years, CHERI provides new mechanisms for software developers and hardware designers to enforce fine-grained memory protection to prevent common bugs

that have plagued computing systems for decades. The authors discuss a CHERI prototype for the Arm processor called Morello that will allow evaluation of the new security enhancements and encourage future adoption.

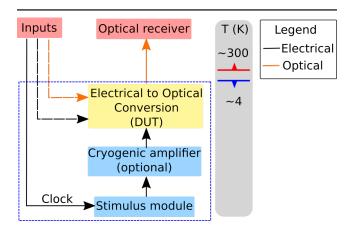

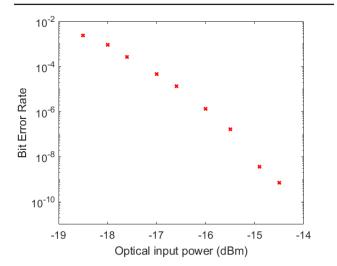

With the end of Moore's Law, new materials and devices will be required to achieve future computing performance gains. Some of these devices will operate at cryogenic temperatures, creating a challenging environment for high-bandwidth interconnects which can dissipate significant heat. The authors of "Evaluating novel interconnects for future cryogenic computers," present their work to establish a test bed for evaluating cryogenic electrical-to-optical devices that provide high-bandwidth data egress from novel devices operating at 4 Kelvin.

Ubiquitous wireless communications protocols and systems have transformed how we communicate. In the article, "Next-generation radio-frequency monitoring in security environments," the authors consider the security risks posed by the wide proliferation of these signals and discuss the RF monitoring requirements to detect and prevent malicious and unintentional emissions that could transmit sensitive data beyond secure facility boundaries.

Localizing faults in today's integrated circuits is essential to improve the manufacturing process but has become extremely challenging due to shrinking feature size and complex fabrication techniques. In "Detecting radio-frequency electric fields with optics," the authors present a novel electro-optic sensor that can detect and localize electric fields with high sensitivity to within less than one millimeter of spatial resolution. These new sensors have potential for a wide range of applications including integrated circuit fault localization and electrical-to-optical conversion of signals.

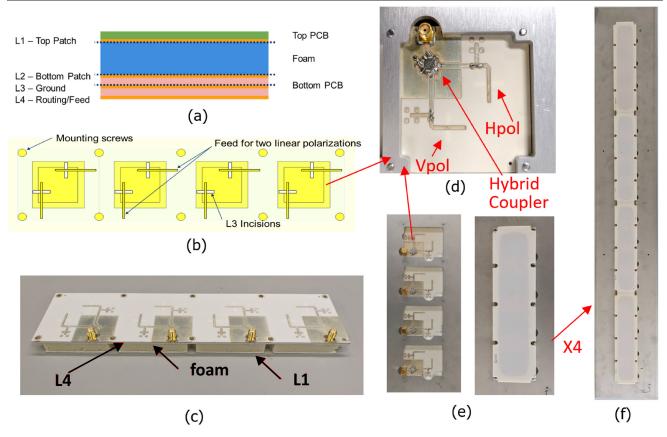

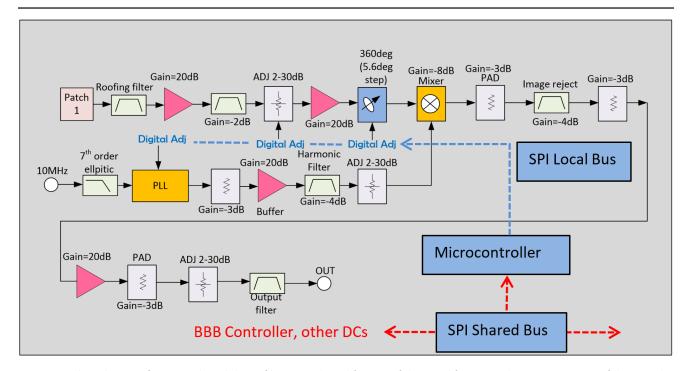

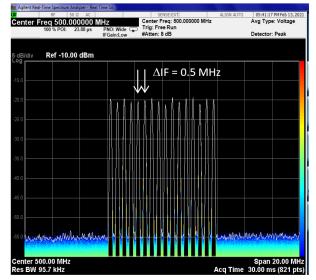

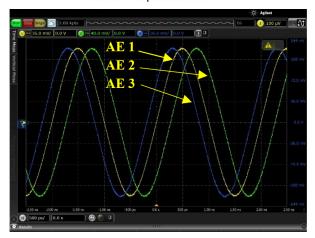

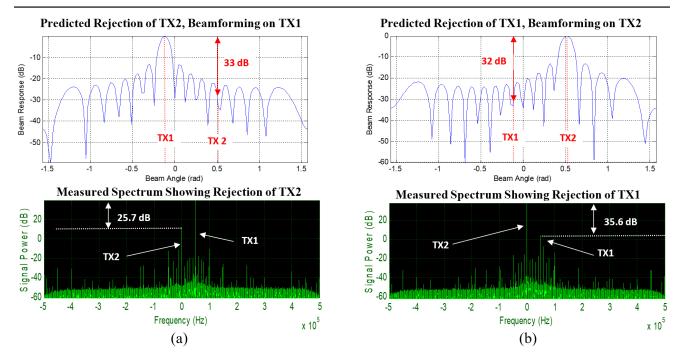

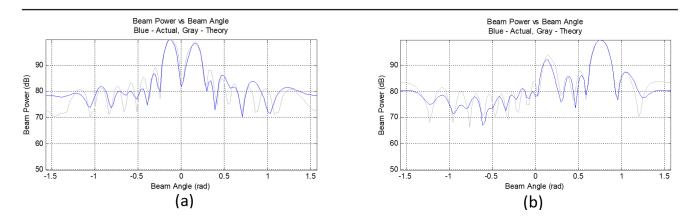

In "A novel hardware concept for digital beamforming: Development and testing of a frequency multiplexed phased array system," the authors describe a novel

multidirectional RF receiver. This receiver offers the benefits of a conventional phased array system such as high-antenna gain/directivity and co-channel interferer suppression, but does so simultaneously across the entire field of view of the array. This enables detection of weak and short duration signals from any direction. The authors present their design methodology, hardware prototype, and system results from a field test.

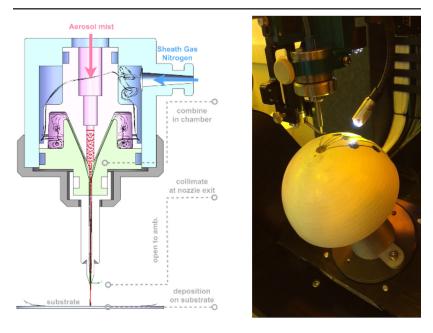

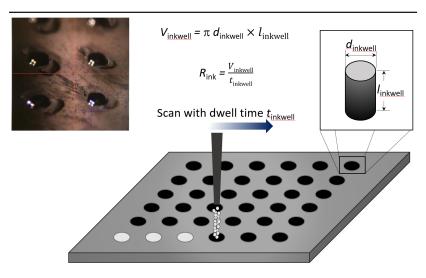

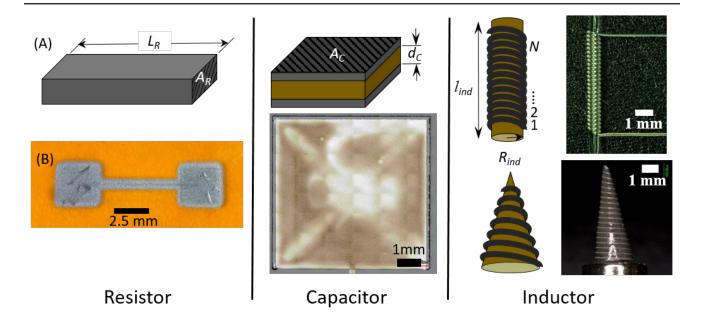

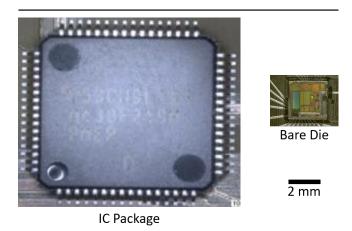

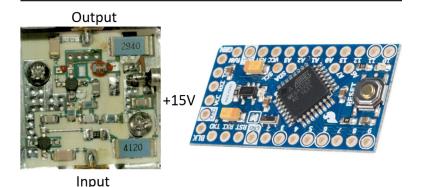

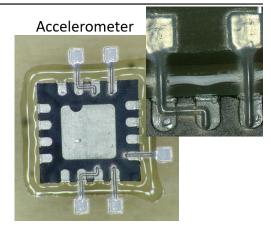

In the final article, "Additive manufacturing of electronic circuits for novel applications," the author discusses new ways to fabricate circuits on nonplanar surfaces to enable electronics and sensors that seamlessly integrate with the geometry of the system and application. The author reviews methods developed at the Laboratory for Physical Sciences for enabling printed electronics and discusses the many benefits including reduced size and weight coupled with the ability to rapidly prototype electronics for field testing.

Advancements in computing and sensing will require flexible architectures, novel hardware devices, and improved sensors that can be integrated together to build systems of the future. The work in this issue illustrates the broad range of research conducted at NSA and with our partners to advance our understanding of these approaches and technologies to enable new mission applications. We thank the authors for their research, which has made this issue of *TNW* possible. We hope you enjoy these articles as much as we enjoyed bringing this issue to print.

#### Robert J. Runser

Technical Director Research Directorate, NSA

David J. Mountain

Advanced Computing Systems Research Directorate, NSA

#### **Contents**

2 The Road Less Traveled: Eliminating Bottlenecks in High-Performance Computing Networking

Sinan G. Aksoy, Roberto Gioiosa, Mark Raugas, Stephen J. Young

10 Improving Security with Hardware Support: CHERI and Arm's Morello

ROBERT N. M. WATSON, PETER SEWELL, WILLIAM MARTIN

22 Evaluating Novel Interconnects for Future Cryogenic Computers

Trisha Chakraborty, Jonathan Cripe, Karen E. Grutter, Gregory S. Jenkins, Kevin D. Osborn, B. S. Palmer, Paul Petruzzi

34 Next-Generation Radio-Frequency Monitoring in Secure Environments

MINH NGUYEN, BRENT LAIRD, MICHAEL R. GROSS

42 Detecting Radio-Frequency Electric Fields with Optics

KAREN E. GRUTTER, PAUL PETRUZZI, SUMI RADHAKRISHNAN

50 A Novel Hardware Concept for Digital Beamforming: Development and Testing of a Frequency Multiplexed Phased Array (FMPA) System

David Elsaesser, Spyro Gumas, Ravi Goonasekeram, Timothy Sleasman, John Marks

64 Additive Manufacturing of Electronic Circuits for Novel Applications

DANIEL R. HINES

73 Selected Publications by NSA Researchers, 2021–2022

The Next Wave is published to disseminate technical advancements and research activities in telecommunications and information technologies. Mentions of company names or commercial products do not imply endorsement by the US Government. The views and opinions expressed herein are those of the authors and do not necessarily reflect those of the NSA/CSS.

This publication is available online at <a href="http://www.nsa.gov/thenextwave">http://www.nsa.gov/thenextwave</a>. For more information, please contact <a href="mailto:jsmarx@uwe.nsa.gov">jsmarx@uwe.nsa.gov</a>.

ISSN 2640-1789 (Print) ISSN 2640-1797 (Online)

# The Road Less Traveled: Eliminating Bottlenecks in High-Performance Computing Networking

Sinan G. Aksoy, Pacific Northwest National Laboratory (PNNL) Roberto Gioiosa, PNNL Mark Raugas, Laboratory for Physical Sciences Stephen J. Young. PNNL

cientific, engineering, and social real-life applications are often too large and complex to fit in a single workstation, both in terms of memory and computing requirements. Generally, a cluster of individual compute nodes interconnected by a high-performance network is required to solve such problems at the required scale. Ideally, such a system would function as if it were one huge computer, but in practice, because of the differences in access speed for local and remote resources, a complete new programming paradigm is required. In particular, because the access time difference between local and remote accesses could be in the order of 10–100x, it is paramount to effectively minimize and/ or hide the latency of remote communication. Additionally, oftentimes multiple compute nodes need to access data on the same remote node (i.e., many-to-one communication patterns), causing network congestion and slowing down the entire application. As a consequence, one of the significant challenges in the use of modern cluster-based supercomputers is how to efficiently, robustly, and quickly handle the necessary communication between the nodes in the cluster. Both current and next-generation supercomputer designs have highly structured network topologies, such as the low-dimensional torus [1], fat tree [2], or DragonFly [3] topology, to have a straightforward routing scheme while attempting to mitigate the traffic congestion in high-communication applications. In many ways, these topologies have evolved and changed in lockstep with the message passing interface (MPI), the dominant programming model for distributed memory supercomputers, and have become tailored for particular classes of problems (i.e., numerical linear algebra and partial differential equations). However, even with modern high-performance network topologies, communication delays are often a significant bottleneck and dominate the overall computation time.

[Photo credit: iStock.com/carterdayne]

s a result of the interaction between the structure of internode communication in various classes of algorithms and the underlying network topologies, certain supercomputers gain a reputation for being more or less suited to a certain class of problems. Specifically, most state-of-the-art supercomputers have been optimized for traditional Linpack-style MPI applications which exchange large messages in highly structured (and often localized) patterns. However, as new problems have emerged that require high-performance computing (HPC) resources, for example, large-scale graph analytics and the training of machine learning models, being able to maintain performance on a more varied collection of communication paradigms has gained in importance. This is especially important to consider when executing on large HPC clusters is the only feasible option for modern graph analytics and machine learning workloads that show computation and memory requirements far beyond those available in a single workstation or small cluster. Of particular relevance to graph analytics and machine learning workloads is the communication performance of HPC systems when sending a large number of small, unstructured, and unpredictable messages. Furthermore, for many of these workloads, the communication patterns are only known at runtime as the computation evolves, making it impossible to predict and mitigate network congestion through smart data layout.

#### Rush hour and computing

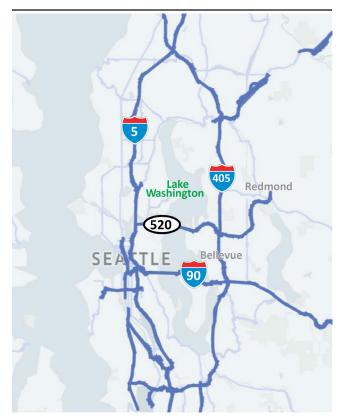

The challenges faced by the HPC community can be understood, by way of analogy, through the evolution of urban transportation traffic. Consider, for example, the Seattle, Washington area. Seattle's arterial road networks, such as the I-5 and I-90 freeways, were developed during the "Boeing Boom." At this time,

the area's largest employers were geographically aligned with the natural traffic pipeline formed by the Puget Sound and Lake Washington. However, as new economic drivers emerged within Seattle, the city has become far more polycentric, with numerous hotspot destinations distributed throughout the region. Seattle's road network now has to contend with a daily influx of traffic from the surrounding Redmond and Bellevue into disparate parts of the city. The resulting traffic patterns are less predictable, less structured, and have (unsurprisingly) led to the development of at least 2,675 documented traffic congestion "hotspots."

While the design of communication architectures for HPC systems doesn't have the geographic limitations of traffic like the greater Seattle area, it is still influenced, much like the traffic network in Seattle, by decades of optimizations for a small class of traffic scenarios. Now that new unstructured traffic scenarios have become more prevalent, the old design paradigms are struggling to provide performance for these new workloads.

Fortunately, rather than having to repeat the decades of effort that went into optimizing HPC systems for MPI-style communications, the HPC communications can take inspiration from an industry that already had to deal with problems of unstructured communication—the telecommunications industry. As early as the 1970's, researchers at Bell Labs and IBM Watson Research Center were thinking about the problem of designing non-blocking switching networks in order to cost-efficiently scale telephone exchanges  $[\underline{4},\underline{5}]$ . Fundamentally, this is a question of how to effectively handle the unpredictable and unstructured telephone communication patterns. Eventually, this line of research coalesced around a single idea as being essential to handling

0010010100100

0101010011010101010101

-210010101110101010111010100101010

101010111010100

**FIGURE 1.** This map of the greater Seattle, Washington area road network with the major motorways (no stoplights) highlighted in blue shows lanes in each direction creating a bottleneck. Lake Washington, to the east of downtown Seattle, significantly impacts the topology of the road network, reducing the capacity and number of east-west routes throughout the region. In fact, between the two floating bridges (I-90 and WA-520), there are only five regular traffic lanes and two high-occupancy vehicle (HOV) lanes in each direction.

the unstructured communications of the telephone system—expansion. While many definitions of expansion have been proposed over the years, they all essentially reduce to the idea that the capacity of the connections leaving any local neighborhood scale with the size of the neighborhood. Returning to our analogy with Seattle traffic, we can see Lake Washington forms a fundamental obstruction to the expansion of the Seattle road network (see figure 1). No matter how you increase the capacity of the two floating bridges crossing Lake Washington, or even if you add new bridges crossing the lake, the capacity of the connection from Seattle to the east side will never be able to scale with the size of Seattle. Essentially, Lake Washington forms a geographic bottleneck and obstruction to expansion for traffic in the Seattle area. Surprisingly, this fairly simple idea of considering networks with no bottlenecks has numerous practical applications from constructing circuits to efficiently perform matrix multiplication, to constructing codes which can effectively correct for errors, to methods to amplify weak sources of randomness to high-quality randomness suitable for practical randomized algorithms.

Given the wide applicability of networks with expansion [6], it is unsurprising that several communication topologies have been proposed which use expansion as a fundamental organizing principle. For example, both the Jellyfish [7] and Xpander [8] data-center architectures rely on expansion properties to provide a robust and extensible communication fabric. However, these topologies are fundamentally random in their construction which presents significant challenges in designing and validating the low-overhead communication schemes necessary in computational applications. In addition, the randomness of the connections presents significant obstacles to the adoptions of these topologies in HPC contexts.<sup>a</sup> In fact, it is likely that the need for lightweight routing schemes (which are facilitated by highly structured topology) has led to the limited expansion properties of in-use and proposed HPC topologies [9]. However, there are known constructions which result in highly structured, optimal expanders [10]. The SpectralFly [11] topology, which we describe in the following section, is based on one such construction.

#### The infinite tree in the forest

Before describing the precise construction of the SpectralFly topology, it is helpful to think about exactly what a network with the best possible expansion (or alternatively, no bottlenecks) would look like. Returning to the traffic analogy, imagine traveling on a road network where every intersection is a four-way intersection. As you approach each intersection, you have four choices—turn around and go back along the road you were traveling on, or continue traveling on one of the other three road segments. Now if the road network has the best possible expansion, those three road segments must lead outside your "local neighborhood." If we imagine continuing along this road network, at each intersection this repeats—you can either turn around or take one of three road segments which leave your "local neighborhood." But as a consequence, the only way

a. In fact, one of the original proposers of the Jellyfish topology, Brighten Godfrey, obliquely referred to this challenge on his blog *You Infinite Snake*, writing "At this point, one natural reaction is that a completely random network must be the product of a half-deranged intellect, somewhere between 'perpetual motion machine' and 'deep-fried butter on a stick."

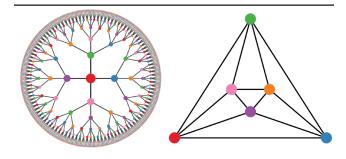

FIGURE 2. (Left) In this optimal expander, every vertex has exactly four connections. Since optimal expanders have no cycles, this unique optimal expander ends up being the four-regular infinite tree. (Right) The vertex colors in this vertex-edge graph for the octahedron are used to generate the vertex colors in the infinite tree (on the left) based on the traversals of the octahedral graph.

to return to an intersection you have already visited is to turn around and go back the way you came. In essence, if the road network has the best possible expansion properties, it must be the four-regular infinite tree (see figure 2).

Obviously, building an infinite tree to use as a road network or as an HPC topology is physically and financially impossible, but taking a slightly different viewpoint on the infinite tree can still provide considerable insight into the properties of networks with good expansion. Specifically, instead of considering the connections in the infinite tree to be physical, we can think about them as a record of decisions made. For example, if we were at the Space Needle in Seattle and wanted to go pick up a coffee at the original Starbucks located at the Pike Place Market, we could either go southwest on Broad Street, turn left on Western Avenue, and continue until we arrived at the Starbucks, or we could go east on Denny Way, turn right on Westlake Ave, and take a right on Stewart Street. While both of these routes will get us some much needed coffee, they emerge from a different sequence of decisions and so would be depicted as different vertices on the infinite tree.

In order to keep track of which locations are the same, we can color individual vertices to encode their location. We see this illustrated in figure 2 where the coloring of the vertices in the infinite tree correspond to the "road network" depicted to the right that has six intersections and 12 roads. For example, in the finite network, the red vertex is adjacent to the green, pink, purple, and blue vertices, and we see that in the infinite tree, every vertex that is colored red is adjacent to a green, pink, purple, and blue vertex. In fact, the correspondence goes deeper than that, as the

colored infinite tree is simply a recording of all the potential routes through the finite network. Indeed, if we start at the red vertex in the finite graph and go to the green vertex, then the pink vertex, and back to the red vertex, in the infinite tree we end up at one of the red vertices in the upper portion of the image of the infinite tree. If, on the other hand, we go to the pink vertex, then the purple, and back to the red vertex, in the infinite tree we end up at one of the red vertices toward the bottom of the infinite tree, despite ending at the same vertex in the finite network. Thus, in many ways, the question of how to design networks with good expansion properties reduces to a perhaps simpler question: *how do you color the vertices of the* infinite tree to preserve the expansion properties of the tree?

To understand what such a coloring looks like, let us consider walking randomly around Seattle. In order to keep track of where we are, imagine every intersection to the west of Lake Washington is colored a different shade of blue, and every intersection to the east of Lake Washington is colored a different shade of red. Since Lake Washington is such a strong bottleneck, it is easy to see that if we start at a blue intersection we should expect to stay on blue intersections for a long period of time. But now think about what this means for the associated colored infinite tree—if we start at a blue vertex, as we go away from that vertex we should typically stay at blue vertices. But there are only so many blue vertices we can use, so that means that the infinite tree must be repeating shades of blue as it grows. In fact, this provides pretty good intuition for comparing two colorings of the infinite tree—a coloring is better at preserving expansion when it is more colorful than another coloring.

Given this framing, it is perhaps not surprising that randomly coloring the vertices of the infinite tree is an effective means of generating graphs with good expansion properties. In fact, this is the approach that is used by the Xpander and Jellyfish topologies to design high-performance data centers. However, this approach has significant drawbacks for HPC needs in that the lack of readily apparent structure in the resulting network means that significant effort needs to be spent in deciding the route any particular communication takes. Providing an explicit means of coloring the vertices of the infinite tree which—in some sense—preserves as much of the expansion property as possible, proved to be a significantly harder challenge.

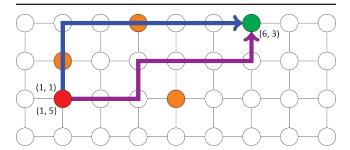

**FIGURE 3.** This figure depicts an idealization of a downtown street network in a grid-like area such as Manhattan, New York. The blue arrow represents the natural path one would take when going from the red intersection to the green intersection, whereas the purple arrow would be one possible path to avoid construction at the orange vertices.

To understand this challenge, it is helpful to return to the problem of navigating around a road network. However, this time instead of focusing on the freeway system, we will focus on navigating around downtown—perhaps some place like Manhattan, New York, where there is a strong grid-like structure such as shown in figure 3. Imagine your friend calls you from the red intersection looking for directions to your favorite coffee shop, conveniently located on all four corners of the green intersection! How would you tell them to get there? You would probably say something like, head north for two blocks and then go east for five blocks. Or perhaps if you knew they were repairing the sidewalks at the orange intersections, you would tell your friend to go east for two blocks, head north for one block, go east for another three blocks, and finally head north for one more block. Now if the picture in figure 3 was instead a diagram of the switches in an HPC topology and you were providing instruction on how to send information from the red switch to the green switch, you would likely express this idea differently (computers not being particularly well known for knowing which way is north, south, east, or west!). Perhaps you would give each switch a name, say the red switch is switch (1, 1) and the green switch is switch (6, 3), and then you would tell the switches to send the information out the port that increases the second coordinate twice, and the first coordinate five times. In fact, most modern and historical HPC topologies can be thought of in this light. Each switch has a "name"—often a vector of integers—and information is routed by performing a sequence of operations on these names, for example increasing or decreasing a coordinate. Oftentimes, there are additional rules which say two different names are effectively the same. For instance, if we

were to imagine connections between the top and bottom row of vertices in <u>figure 4</u>, we would want to say that (1, 5) is an alternative name for the red vertex, as starting there and increasing the second coordinate four times would return us to the red vertex. Thus, the real challenge is to design a naming scheme for the infinite trees and operations on those names which maximize the colorfulness of the infinite tree.

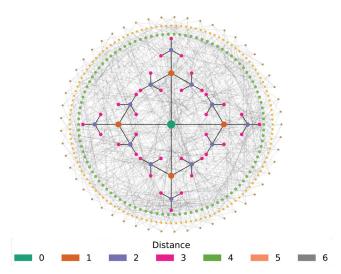

In the late 1980's, Lubotzky, Phillips, and Sarnark [12], and independently Margulis [13], provided a relatively simple naming scheme and set of operations to provide an optimal coloring scheme for a wide range of infinite trees and number of colors. The collection of names for every vertex is a list of two-by-two matrices with integer entries, and the operation going from one name to another is multiplication by one of a handful of two-by-two matrices. The SpectralFly topology is defined by using one of these networks as the interconnection network between the switches and then placing an appropriate number of compute nodes at each switch (see figure 4).

The fact that the colorings proposed by Lubotzky, Phillips, and Sarnak [12] are the best possible at preserving the expansion properties of the infinite tree relies on a deep result in the representation theory of automorphic forms originally conjectured by Ramanujan [14]. However, we can gain some intuition as to why their rules result in more colorful trees by comparing the operations with other topologies. For example, since the operation for the torus topology is incrementing/decrementing individual coordinates, the end location depends only on the number of increments/decrements per coordinate, not the particular order they are applied. In contrast to this, the results of matrix multiplication (in general) rely on the order of operations. That is, by applying the same set of operations in two different orders, it is possible to arrive in different locations. In figure 5 we can see the difference in colorfulness in the infinite tree for torus topology and the SpectralFly topology.

# Structural comparison with SpectralFly topology

The SpectralFly topologies promise as supercomputing topology is evidenced by its exceptional structural properties. We now put these properties in perspective, by comparing them against those of two well-known topologies: a DragonFly network and a

**FIGURE 4.** In this depiction of the connections between switches for a 336-switch SpectralFly topology with four intra-switch connections per switch, the switches are color coded by distance from a central switch, highlighting the tree-like neighborhood of the switch.

torus mesh. We consider a small, sparse SpectralFly network on 120 nodes and 240 links. To ensure a fair comparison, we optimally select<sup>b</sup> the parameters of a DragonFly topology on exactly the same number of nodes and edges, and a two-dimensional torus mesh on 121 nodes and 242 edges. This near-exact three-way match enables a size agnostic comparison: each network starts with the same number of nodes, links, and radix, but makes different design choices in assembly.

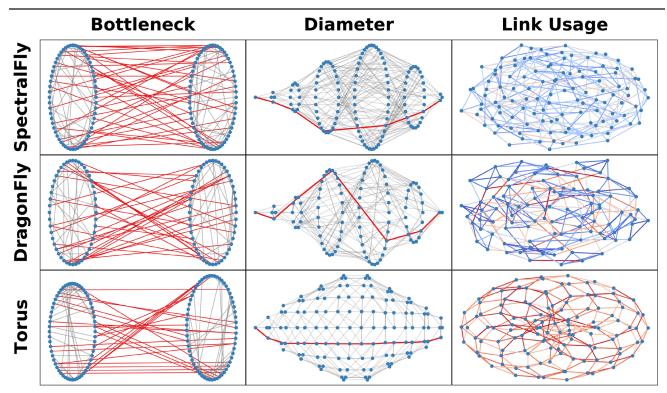

The three networks are visualized in <u>figure 6</u>. Each row of <u>figure 6</u> plots the same network, but with one of three different structural properties emphasized: the tightest bottleneck, the network diameter, and link usage frequencies in random traffic. Each of these structural properties are fundamental for supercomputer design: bottleneckness measures congestion proneness, diameter is a proxy for worst-case latency, and link usage patterns impact link-contention.

#### **Bottlenecks**

The first column of <u>figure 6</u> presents a split of each topology into equal parts which minimizes the number of edges crossing (in red), as found by METIS software [16]. For SpectralFly, Dragonfly, and torus, this yields 40, 31, and 26 links crossing,

FIGURE 5. In this comparison of an infinite tree for a two-dimensional torus topology (left) and a SpectralFly topology with parameters (3,7) (right), the vertices of both are colored using the same equally spaced gradient. The vertex color corresponds to the order the vertices are discovered in the process; earlier vertices are colored blue and later vertices are colored red. As we can see, the torus topology is significantly less colorful than the SpectralFly topology, indicating that the SpectralFly topology has significantly better expansion properties.

respectively. In practice, this means that when there are many messages, we would expect the communication delays to be about 24% smaller as compared to DragonFly, and 35% smaller as compared to the torus.

#### Diameter

Figure 6's second column visualizes paths linking a source-destination pair furthest from each other in the network—the length of which is known as the network diameter. The *k*-th ring of vertices from the leftmost contains all those that can be reached from that vertex in *k* hops. Small diameters ensure any vertex can be reached quickly from any other. In this case, both SpectralFly and DragonFly have an identical diameter of 6, while the torus has a diameter of 10.

#### Link loading

We simulate unstructured traffic on each network by randomly selecting 5,000 source-destination pairs in each network, and then routing via a minimal path. In the case that there are multiple such minimal paths, we select one at random. For each link in the network, we count the number of times it was traversed. Figure 6 presents the distribution of these link usage counts. For SpectralFly, this distribution is highly symmetric and tightly concentrated, reflecting that edges are evenly spread across the network.

b. In particular, we generate a DragonFly topology with height h=1, g=24, groups of size a=4. We optimally allocate the intergroup edges as suggested by Teh, Wilke, Bergman, and Rumley [15].

**FIGURE 6.** These graph visualizations emphasize different structural properties for three similarly-sized SpectralFly, DragonFly, and torus instances, each on about 120 nodes and 240 edges. The first column emphasizes the expansion, the second column emphasizes the diameter, and the third column emphasizes the prevalence of edges on shortest paths.

DragonFly, on the other hand, is the opposite and has a long tail: some edges are used heavily while others are almost never used. Lastly, as with SpectralFly, the link usage counts for the torus are also tightly concentrated, but overall larger: due to the torus' larger diameter, paths linking vertices tend to be longer and edges get used more frequently, albeit evenly, across the network. These observations are also reflected in the network visualization: each edge is colored on a blue-to-red scale, according to its percentile within the observed link counts aggregated across all three networks. Accordingly, SpectralFly and the torus' edges are homogeneous in color; whereas, those in Dragonfly run the gamut.

#### **Conclusions and future work**

As the workloads executed on current and future HPC systems evolve to include nontraditional workloads, such as data analytics and artificial intelligence (AI)/machine learning, so should the systems themselves. We argue that HPC systems should move away from

highly structured networks optimized for regular and large message communication to networks such as SpectralFly that expand and dynamically remove bottlenecks, and hence adapt to the irregular and unpredictable nature of the workloads. This move however would be onto a road less traveled, and as such, will require strong evidence that it can efficiently support emerging application domains before industry will commit to investing in it. At Pacific Northwest National Laboratory, we have developed and used several tools, based on MPI and partitioned global address space (PGAS), to analyze different network designs. The results indicate that SpectralFly networks are not only better at supporting irregular communication typical in data analytics and AI/machine learning, but that they might also outperform traditional networks when executing regular applications (unless they heavily rely on near-neighbor communication). In other terms, the SpectralFly network will let you sip your much deserved, end-ofthe-day coffee at your favorite coffee shop without spending hours stuck in the car on the streets of Seattle downtown.

#### References

- [1] Adiga NR, Blumrich MA, Chen D, Coteus P, Gara A, Giampapa ME, Heidelberger P, Singh S, Steinmacher-Burow BD, Takken T, Tsao M, Vranas P. "Blue Gene/L torus interconnection network." IBM Journal of Research and Development. 2005;49(2-3):265-276.

- [2] Leiserson, CE. "Fat-trees: Universal networks for hardware-efficient supercomputing." *IEEE Transactions* on Computers. 1985;C-34(10);892-901. doi: 10.1109/ TC.1985.6312192.

- [3] Kim J, Dally WJ, Scott S, Abts D. "Technology-Driven, Highly-Scalable Dragonfly Topology." SIGARCH Computer Architecture News. 2008;36(3):77–88. doi: 10.1145/1394608.1382129.

- [4] Chung FRK. "On concentrators, superconcentrators, generalizers, and nonblocking networks." The Bell System Technical Journal. 1979;58(8):1765-1777. doi: 10.1002/ j.1538-7305.1979.tb02972.x.

- [5] Pippenger N. "Superconcentrators." SIAM Journal on Computing. 1977;6(2):298-304. doi: 10.1137/0206022.

- [6] Hoory S, Linial N, Wigderson A. "Expander graphs and their applications." Bulletin of the American Mathematical Society. 2006;43(4):439-561. doi: 10.1090/ S0273-0979-06-01126-8.

- [7] Singla A, Hong C, Popa L, Godfrey PB. "Jellyfish: Networking data centers randomly." In: 9th USENIX Symposium on Networked Systems Design and Implementation (NSDI 12); 2012. Available at: https:// www.usenix.org/system/files/conference/nsdi12/nsdi12-final82.pdf.

- [8] Valadarsky A, Shahaf G, Dinitz M, Schapira M. "Xpander: Towards optimal-performance datacenters." In: Proceedings of the 12th International on Conference on Emerging Networking Experiments and Technologies; 2016, pp. 205-219. doi: 10.1145/2999572.2999580.

- [9] Aksoy SG, Bruillard P, Young SJ, Raugas M. "Ramanujan graphs and the spectral gap of supercomputing topologies." The Journal of Supercomputing. 2021;77(2):1177-1213. doi: 10.1007/s11227-020-03291-1.

- [10] Alon N. "Eigenvalues and expanders." Combinatorica. 1986;6(2):83-96. doi: 10.1007/BF02579166.

- [11] Young S, Aksoy S, Firoz J, Gioiosa R, Hagge T, Kempton M, Escobedo J, Raugas M. "SpectralFly: Ramanujan graphs as flexible and efficient interconnection networks." In 2022 IEEE International Parallel and Distributed Processing Symposium (IPDPS), Lyon, France, 2022 pp. 1040–1050. doi: 10.1109/IPDPS53621.2022.00105.

- [12] Lubotzky A, Phillips R, Sarnak P. "Ramanujan graphs." Combinatorica. 1988;8(3):261-277. doi: 10.1007/ BF02126799.

- [13] Margulis GA. "Explicit group-theoretical constructions of combinatorial schemes and their application to the design of expanders and concentrators." Problemy Peredachi Informatsii. 1988;24(1):51-60.

- [14] Ramanujan S. "On certain arithmetical functions." Transactions of the Cambridge Philosophical Society. 1916;22(9):159-184.

- [15] Teh MY, Wilke JJ, Bergman K, Rumley S. "Design space exploration of the dragonfly topology." In: Kunkel J, Yokota R, Taufer M, Shalf J (Eds), High Performance Computing. ISC High Performance 2017. Lecture Notes in Computer Science (LNTCS), vol 10524. Springer, Cham. Available at: https://doi.org/10.1007/978-3-319-67630-2\_5.

- [16] Karypis G, Kumar V. "A fast and high quality multilevel scheme for partitioning irregular graphs." SIAM Journal on Scientific Computing. 1998;20(1):359–392. doi: 10.1137/ S1064827595287997.

# Improving Security with Hardware Support: CHERI and Arm's Morello

Robert N. M. Watson, University of Cambridge Peter Sewell, University of Cambridge William Martin, National Security Agency

he CHERI project, from the University of Cambridge and SRI International, extends instruction-set architectures (ISAs) with unforgeable architectural capabilities, to be used in place of conventional machine-word addresses to access memory. CHERI, which stands for Capability Hardware Enhanced Reduced Instruction Set Computer (RISC) Instructions, deterministically protects C/C++ pointers and other references, and also enables in-addressspace software sandboxing. With changes to the compiler and operating system (OS), CHERI enables new hardware-software security protection models for existing software (typically with only very minor changes for memory safety):

- Deterministic fine-grained C/C++ memory protection at low overheads; and

- Scalable software compartmentalization, including sandboxed libraries, with interprocess communication performance improvements and function-call-like domain transition.

In a 2020 blog post evaluating CHERI, the Microsoft Security Response Centre (MSRC) wrote: "We've assessed the theoretical impact of CHERI on all the memory safety vulnerabilities we received in 2019, and concluded that in its current state, and combined with other mitigations, it would have deterministically mitigated at least two thirds of all those issues"[1]. Scalable single-address software sandboxing has the potential to mitigate many more, and to enable a more disruptive shift to stronger compartmentalized software architectures.

Arm has recently developed the Morello architecture and processor, incorporating the CHERI protection model into a contemporary high-performance Arm design. Morello is an experimental prototype extending the existing Armv8-A architecture and Neoverse N1 64-bit processor design to support CHERI research and evaluation on the path to eventual productization, and to demonstrate the viability of the CHERI technology using real commercial processes and manufacturing. Extensive software porting is establishing feasibility. Development boards are available for research and prototyping as of early 2022, and are already running significant open-source software stacks, such as an adapted version of the FreeBSD OS and KDE desktop stack running with strong memory safety [2].

In this article we give an overview of CHERI and Morello, and pointers to full discussions elsewhere. It is based largely on material from the "Introduction to CHERI" [3] and "Verified security for the Morello capability-enhanced prototype Arm architecture" [4] technical reports; it does not contain new research results.

#### Introduction

Memory safety bugs continue to be a major source of security vulnerabilities, responsible, for example, for around 70% of those addressed by Microsoft security updates and around 70% of the high-severity bugs impacting Chromium [5, 6]. Their root causes are well-known legacy design choices and limitations of normal practice that date back to the 1960s and 1970s including: processor architectures that permit one to access any memory location via its plain numeric machine address, protected only via the coarse-grain mechanisms of virtual memory; systems programming languages such as C and C++ that let one do memory accesses without further static or dynamic protection; and test-and-debug development methods that cannot provide high assurance. All of these are baked into the critical systems codebase across the industry, and the result, in today's adversarial environment, is that our codebase inescapably contains many programming errors, which all too often lead to exploitable vulnerabilities.

Many approaches have been developed to improve this situation, from better software engineering processes, through better bug-finding tools and better programming languages, to techniques for machine-checked mathematical proofs of correctness and security. All these are worthwhile, but the legacy investment, the need for systems code to work close to the machine, and the inability of bug-finding to provide high assurance has made it very hard to radically improve conventional systems. Best practice remains an endless Red Queen's Race of identifying and patching security vulnerabilities where one can.

Over the last 10 years, the CHERI project [7] has been exploring a new approach to substantially improve the security of mainstream systems. The basic idea is simple: rather than accessing memory locations via plain numeric machine addresses (and using those to implement C/C++ pointer values), provide architectural support for unforgeable capabilities that let one do an efficient permission check at access time (capability systems of various kinds also date back to the 1960s). This, with additional mechanisms, lets one enforce fine-grained memory protection and highly scalable software compartmentalization. Crucially, achieving this memory protection requires only relatively modest changes to architectures and processor designs and relatively minor changes to the sources of existing C/C++ systems software, so there is a real prospect of it becoming widely deployable.

For example, a recent study found that 0.036% lines of code in adapted portions of the Wayland, Qt, and KDE open-source Windows-system and desktop software stack required changes to compile and run with CHERI C/C++ [2].

The academic results for CHERI are encouraging, but achieving such adoption first needs an industry-scale evaluation to demonstrate viability and enable that pull, and that needs a high-performance silicon processor implementation and software stack above it. This is beyond what can be done academically, but hard to justify as a purely commercial project. The 2019-24 UK Research and Innovation (UKRI) Digital Security by Design (DSbD) challenge resolves this chicken-and-egg difficulty with a combined public-sector and industry program (in excess of \$200 million) to build and evaluate such a demonstration platform and support research and development above it [8]. Arm, in a consortium with the University of Cambridge, University of Edinburgh, and Linaro, supported in part by DSbD, has designed and built Morello, a CHERI-enabled prototype architecture, processor, system-on-chip (SoC), development board, and software stacks, extending the Army8.2-A architecture and the high-performance Neoverse N1 processor [9, 10]. The architecture, emulators, and software toolchains have been available since 2019, and boards began to ship to academic, industrial, and government research labs in early 2022. This will allow evaluation of CHERI mechanisms in a variety of configurations and use cases on a state-of-the-art hardware platform, and paves the way for the potential adoption of CHERI into future production architectures and devices.

CHERI is, most unusually, a hardware/software/semantics codesign project. It is centered around a few core principles and architectural ideas that can be instantiated to a range of conventional architectures, explored in detail to date for MIPS, RISC-V, Arm-A, and Arm- M, and sketched for x86. Based on these, there is microarchitectural hardware innovation to implement these efficiently; programming language work so that existing C and C++ code can be rebuilt to gain the additional protection with minimal porting cost; systems software work to demonstrate that OSs, language runtimes, and applications can be adapted to CHERI; and formal semantics and verification work to establish with high confidence that these new architecture variants do indeed provide the intended security properties. The latter includes machine-checked mathematical proofs (in the Isabelle

proof assistant) of key security properties of the complete sequential CHERI-MIPS and Morello ISA specifications  $[\underline{11},\underline{4}]$ —the first time this has been possible for modern production architectures.

CHERI has been designed from the outset to make widespread adoption feasible, but there is a long path and a great deal of work to get any substantial new architectural feature deployed. CHERI has been supported by a sequence of Defense Advanced Research Projects Agency (DARPA) projects, from 2010 onward, by the UK government Engineering and Physical Sciences Research Council (EPSRC) funding, by an EU European Research Council (ERC) Advanced Grant, and by grants and donations from Arm, Google, and others, leading up to the Morello program supported by the UK government DSbD funding, Arm, and others.

CHERI has also been informed by (and builds on) two early research collaborations with the NSA in the early 2000s. First was the collaboration by NSA with Robert Watson at Trusted Information Systems (TIS), centered on Type Enforcement (TE) and OS access control. Robert Watson led the Security-Enhanced Berkley Software Distribution (BSD) and Security-Enhanced Darwin work at TIS, developing and transitioning concepts about operating-system structure, containment, and sandboxing to widespread use through FreeBSD, macOS, iOS, and Junos. At Cambridge, his focus turned to finer-grained software compartmentalization within rather than between applications, leading to the Google-supported development of Capsicum [12], an OS capability framework supporting application decomposition for security, and in turn to the limitations of current processor architectures. A second NSA research collaboration, with Mike Gordon and Anthony Fox at Cambridge, focused on formal modeling of Arm and other ISAs in the HOL4 interactive theorem prover. This work led to the L3 ISA modeling language, which was used in the CHERI-MIPS development and verification, and which was a precursor of our Sail language [13], used for the definitions of RISC-V and CHERI-RISC-V, and in the Morello ISA verification.

#### An overview of CHERI

The basis of CHERI is a modest set of *architecture extensions* adding hardware representations for capabilities and instructions for manipulating them, integrated into a conventional ISA. Then there are microarchitectural hardware implementation

innovations, developed in our CHERI-MIPS and CHERI-RISC-V FPGA implementations and Arm's Morello silicon implementation; software model and CHERI C/C++ innovations to let software benefit from the new hardware support; CHERI systems software adapting substantial bodies of legacy software; and CHERI formal semantics and verification that increase assurance in the architecture design and inform CHERI C/C++.

#### CHERI architecture extensions

CHERI extends conventional ISAs, which use machine words to represent language-level integers and pointers, with a new type of hardware-supported data, *unforgeable capabilities* [14, 15, 16, 17]. Capabilities can be used to protect (virtual) addresses intended to be used as code or data pointers—those arising from source-language pointers and also those used in the underlying implementations of language features such as local and global variables, thread-local storage, return addresses, C++ virtual table pointers, and interlibrary linkage. All memory accesses, including loads, stores, and instruction fetch, must be authorized by a capability. As with existing kinds of hardware-supported data (e.g., integers, floats, vectors), capabilities are held in registers and in memory; they are loaded, stored, and manipulated using new capability-aware instructions.

In a 64-bit CHERI ISA [18], instead of using simple 64-bit machine-word virtual-address pointer values to access memory, restricted only by the memory management unit (MMU), one can use 128+1-bit capabilities containing a virtual address together with the base and bounds of the memory it can access, and permissions and other metadata. A sophisticated compression scheme lets all this be encoded within the capability with acceptable precision [19]. In turn, having the data within the capability enables a fast access-time check (without any additional lookup). faulting if there is a safety violation. A one-bit tag per register and per each capability-sized and aligned unit of memory, cleared in the hardware by any non-capability write (and not directly addressable), ensures capability integrity by preventing forging. Legacy code compiled without capabilities can still access memory via machine words, but these are restricted by default capabilities held in specific registers, so all accesses can be controlled. This architectural mechanism, along with additional sealed-capability features for secure encapsulation, can be

used by programming language implementations and systems software in many ways.

The ISA design lets code shrink the rights associated with capabilities but never grow them: a capability monotonicity property. When any instruction constructs a new capability (except in sealed capability manipulation and exception raising), it cannot exceed the permissions and bounds of the capability from which it was derived. That implies reachable capability monotonicity: in any execution of arbitrary code, until execution is yielded to another domain, the set of reachable capabilities (those accessible to the current program state via registers, memory, sealing, unsealing, and constructing sub-capabilities) cannot increase.

At boot time, the architecture provides initial capabilities to the firmware, allowing data access and instruction fetch across the full address space. Additionally, all tags are cleared in memory. Further capabilities can then be derived (in accordance with the monotonicity property) as they are passed from firmware to boot loader, from boot loader to hypervisor, from hypervisor to the OS, and from the OS to the application. At each stage in the derivation chain, bounds and permissions may be restricted to further limit access. For example, the OS may assign capabilities for only a limited portion of the address space to the user software, preventing use of other portions of the address space.

Similarly, capabilities carry with them *intentional*ity: when a process passes a capability as an argument to a system call, the OS kernel can carefully use only that capability to ensure that it does not access other process memory that was not intended by the user process—even though the kernel may in fact have permission to access the entire address space through other capabilities it holds. This is important as it prevents "confused deputy" problems, in which a more privileged party uses an excess of privilege when acting on behalf of a less-privileged party, performing operations that were not intended to be authorized. For example, this prevents the kernel from overflowing the bounds on a userspace buffer when a pointer to the buffer is passed as a system-call argument.

These architectural properties provide the foundation on which a capability-based OS, compiler, and runtime can implement C/C++-language memory safety and compartmentalization.

Compatibility with current designs has been essential to our approach: CHERI composes well with contemporary architectures, microarchitectures, compiler implementations, OS design, and application structure. The software constructs resting on virtual memory—processes and virtual machines—persist, but are augmented by new mechanisms and structures that support CHERI's protections.

#### CHERI Hardware

A principal design goal of the CHERI architecture has been to add new architectural primitives with only limited impact on the overall microarchitecture of contemporary processor and memory-subsystem designs. We have explored potential approaches to integrating CHERI into multiple microarchitectures including our locally developed pipelined Bluespec Extensible RISC Implementation (BERI) 64-bit MIPS core and the Bluespec Piccolo, Flute, and Tooba RISC-V cores; Arm has built on these ideas in Morello. There are two key microarchitectural challenges:

- ▶ **Tagged memory:** Conventional dynamic random-access memory (DRAM) does not support capability tagging. Architecturally, the CHERI protection model does not require a particular implementation of tagging, just that tags be suitably protected and properly coherent with the data they protect. In early designs, we used a simple look-aside tag table stored in DRAM and maintained by the memory controller along with a cache; however, performance analysis revealed a significant DRAM access-rate overhead to this approach. This led us to design a hierarchical tag table able to benefit from the non-uniform distribution of capabilities in memory: inevitably, some pages are rich in capabilities (e.g., stacks, vtable storage); whereas, others are not (e.g., memory mapped files, video and image data) [20]. Another option is to reuse additional metadata storage present in more contemporary double data rate (DDR) designs, including bits available for use in error-correction code (ECC), to hold tags.

- ▶ Capability compression: In the absence of capability compression, CHERI capabilities would be four times, rather than two times, the native address size, given the need to store three separate virtual addresses (bottom bound, capability address, and upper bound) as well as metadata.

Bounds compression, which exploits redundancy between these three addresses, is therefore essential to reducing the dynamic memory footprint of pointer-intensive applications (such as language runtimes). Developing a compression scheme that balanced software requirements for precision with microarchitectural efficiency was a significant challenge [19].

Apart from these, CHERI has been designed to avoid changing fundamental design choices in current architectures and microarchitectures—essential elements such as pipeline structure, memory subsystem designs including caches, MMUs, and so on, retain their current structure.

#### CHERI software model and CHERI C/C++

CHERI capabilities are an architectural primitive that can be used for a variety of software purposes up and down the software stack, with potential uses in firmware and boot loaders, OSs, language runtimes, CHERI-specific compartmentalization libraries, and compiler-generated code for the C and C++ application programs [17, 21, 22, 23, 24, 25]. In our research, we have pursued two central use cases of CHERI capabilities within current C/C++-language software stacks:

- ▶ Fine-grained memory protection: By utilizing capabilities instead of integers to implement C/C++ language pointers, and through modest extensions to the OS and language runtime, we have implemented strong and efficient spatial, referential, and (optionally) temporal memory safety for these traditionally memory-unsafe languages.

- ▶ Scalable software compartmentalization:

Capabilities provide an alternative means to

construct the software isolation and controlled

communication required to implement compartmentalized software designs. Unlike MMUbased compartmentalization (i.e., implemented

using virtual memory), capability-based techniques allow for more granular and scalable

data sharing, as well as a single-address-space

programming model.

#### Fine-grained memory protection

The underlying principle in CHERI C and C++ memory protection is to implement pointers (both explicit in the language and implied in the runtime

environment) using capabilities. The main CHERI dialects of C and C++ implement all C/C++ pointer types, as well as all implied pointers (e.g., return addresses, the stack pointer, and so on) using capabilities. This changes the application binary interface (ABI), as pointer size has increased, changing the in-memory layout of data structures, etc., just as 64-bit code has a different ABI from 32-bit code. Because pointers and integers are implemented using different types, additional care must be used so that pointer values retain tags where intended; for example, the C type uintptr\_t (implemented using the hardware capability type) must be used to hold values that could be integers or pointers, as *long* (implemented using the hardware integer type) has room only for the address portion of a pointer, not its metadata and tag. Overall, however, relatively little code experiences disruption with the introduction of strong memory safety.

To a first approximation, where in classic C/C++ an access by buggy code to arbitrary memory would be undefined behavior with respect to the language standard and, in practice, might lead to an exploitable vulnerability, in CHERI C/C++ such an access will raise a capability exception.

This gives spatial protection; additional work shows how one can also guarantee *temporal safety* (e.g., against reuse-after-free errors) above CHERI architectures, with data so far suggesting reasonable overheads for heap temporal safety.

In addition, we support *hybrid-capability code*, with dialects that implement pointer types using integers by default, interpreted with respect to a global default data capability (DDC) able to address code, globals, heap, and stack(s).

#### Scalable software compartmentalization

Conventional MMU-based software compartmentalization decomposes larger software applications into components that run in isolated processes, linked only by controlled communication implemented using inter-process communication (IPC). This widely deployed technique, found in applications ranging from Google's Chromium web browser to most Apple iOS applications, limits the impact of software compromise by reducing rights and further attack surfaces available to attackers. This technique is especially important because it provides resilience in the presence of not only exploits for unknown vulnerabilities in known classes (such as buffer overflows), but also

protects against future as-yet undiscovered classes of vulnerability and exploit techniques. However, MMU-based compartmentalization designs impose substantial scalability limits due to utilizing multiple address spaces and page-granularity sharing: the number of compartments and their communication is severely limited, with performance significantly impacted as the number of compartments and their communication grow.

CHERI capabilities permit the construct of isolation and controlled sharing within address spaces, offering potentially greater compartmentalization scalability. Compartments are constructed utilizing closed graphs of capabilities, in which an executing compartment has no access to the resources of other compartments nor broader system memory. Bounds and permissions ensure that capabilities assigned to compartments grant access only to intended resources; monotonicity ensures that these rights cannot be modified to include other resources. Temporal safety is important to ensure that data and capabilities do not improperly leak between compartments when memory is freed and reused.

Switching between compartments can be implemented using one of two architectural mechanisms for controlled non-monotonicity: exception handling, which gives access to additional exception-handling capabilities; or a special jump instruction (CInvoke) that atomically unseals and jumps to a pair of code and data capabilities whose object types match. Both architectural mechanisms provide a means by which available capabilities can be widened, but only when executing previously determined code paths. The jump-based mechanism avoids the cost of exceptions (which is microarchitecturally significant) and avoids the need for a privileged ring transition. It also allows the possibility of more scalable software designs multiple implementations of domain transition can coexist within a single address space.

The semantics of protection domains and domain transitions are flexible, as these architectural primitives support a variety of potential software uses. These include synchronous function-call-like semantics for domain transition, as well as asynchronous message passing. Compartmentalization models could more resemble libraries in the former case and processes in the latter, depending on the implementation.

#### CHERI systems software

We have developed a reference software stack for the CHERI architecture exploring several key software design dimensions opened up by capabilities. This work has had a number of aims, including playing an essential part in our hardware-software codesign effort to develop CHERI, to allow evaluation and demonstration of the CHERI approach at scale, and to act as templates for use. The reference stack includes the following components.

- ▶ CHERI Clang/low-level virtual machine (LLVM)/low-level design (LLD): An extended version of the Clang/LLVM compiler suite and LLD linker that are able to compile and link hybrid-capability and pure-capability code for multiple CHERI-enabled architectures.

- ▶ CHERI GDB: An extended version of the GNU debugger (GDB) that is able to debug hybrid-capability and pure-capability code on multiple CHERI-enabled architectures.

- **CheriBSD kernel:** An extended version of the FreeBSD OS whose kernel can be compiled either as hybrid-capability or pure-capability code, offering different degrees of kernel memory protection. The CheriBSD kernel is also able to host legacy, hybrid-capability, and pure-capability userspace environments. The pure-capability process environment is known as CheriABI, and is a new OS ABI based on ubiquitous userspace use of architectural capabilities. CheriBSD is also able to offer optional temporal memory safety for (non-stack) allocations in pure-capability userspace applications. CheriBSD's colocated process (or coprocess) model allows multiple userspace processes to coexist safely within a shared virtual address space, using CHERI facilities for fast memory sharing and kernel-free context switching. CheriBSD also implements a CHERI-extended version of FreeBSD's bhyve Type-2 hypervisor, and is able to host CHERI-enabled guest virtual machines.

- CheriBSD hybrid userspace: An extended version of the FreeBSD userspace that is minimally modified to support hybrid-capability code execution, including modest additions to the C runtime (CRT) and system libraries (including libc).

- CheriBSD CheriABI userspace: An extended version of the FreeBSD userspace that supports pure-capability execution with modest further extensions.

- ▶ CheriBSD applications: A set of extended applications able to operate in the CheriABI process environment, including integrated FreeBSD programs such as open-source secure shell (OpenSSH), and also third-party applications such as Apple's WebKit, the PostgreSQL database, and X11 window system. These all operate with full spatial, referential, and temporal memory safety.

- ▶ CheriFreeRTOS: An extended version of the embedded open-source real-time OS (FreeRTOS) that is able to be compiled as pure-capability code, offering spatial and referential memory safety, as well fine-grained software compartmentalization with fault recovery.

- CheriOS microkernel: An experimental CHERIspecific nanokernel and microkernel illustrating a potential set of design choices available when CHERI is an essential part of an OS design, and its use is maximized. This is a single-address-space, asynchronous message-passing OS intended to support extremely granular compartmentalization side-by-side with strong memory safety.

This software stack demonstrates a number of points in the design space. It explores varying degrees of incorporation and adoption of CHERI protection illustrating CHERI's incremental adoptability properties. It also illustrates architectural neutrality for both the CHERI protection model and software designed for it.

#### CHERI formal semantics and verification

Formal modeling and verification are essential parts of the CHERI engineering process and of the resulting artifacts. Our CHERI extensions to the 64-bit MIPS and 32/64-bit RISC-V ISAs are defined in the Sail modeling language [13] (with CHERI-MIPS previously in L3 [26]). Sail is a clean, engineer-friendly, first-order imperative language for ISA specification with lightweight dependent types [type-checked using satisfiability modulo theories (SMT)] for static type-checking of bit-vector lengths. It has also been used to give complete sequential ISA definitions for ARMv8-A (automatically translated from the Arminternal ASL definition [27]) and for RISC-V, and for

ISA semantics integrated with architectural concurrency models. The Sail CHERI architecture models are available as open source.

Sail and L3 are used to generate from these primary models:

- ▶ Reference documentation, automatically incorporated into the CHERI ISA specification [14];

- Executable ISA-level simulators, in C and OCaml, used as oracles to test hardware against and for software bring-up;

- ► Hardware instruction test cases [28], used for hardware testing;

- SMT-LIB definitions of the architecture, used for SMT checking of intended properties; and

- ▶ Theorem-prover definitions of the architecture, in Coq, Isabelle/HOL, and HOL4, used to state and prove security properties.

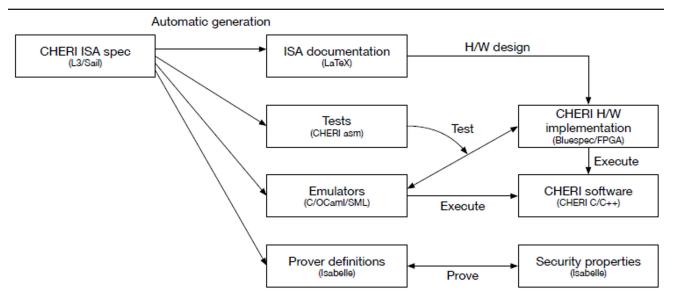

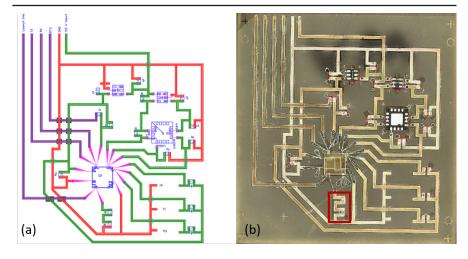

Figure 1 illustrates these and how they are used in the CHERI engineering process. Importantly, developing these Sail and L3 definitions did not require expertise in semantics or theorem proving, so the researchers and engineers who would otherwise write a prose/pseudocode architecture document could write and own them. As is familiar from other uses of formal specification, this low-cost activity already brought several benefits, even before any proof work was undertaken.

For CHERI-MIPS and Morello, we have proved that the architecture design does satisfy the intended reachable capability monotonicity property described above—that arbitrary code, if given some initial permissions, cannot increase those during its execution (up to the point of any domain transition) [11, 4]. We have also captured the guarantees one has (and the required assumptions) when executing an untrusted subprogram within a controlled isolation boundary.

These are machine-checked mathematical proofs, using the Isabelle proof assistant. This gives a level of confidence that is not achievable with testing alone—indeed, the highest level of assurance possible.

For formal statements and proofs of security properties, it is always crucial to understand exactly what force they have. We should emphasize that these are properties of the architecture designs, the ISA specifications. It is especially important to ensure that those have the intended properties, as otherwise one would be building vulnerabilities into any

**FIGURE 1.** The main artifacts of the CHERI-RISC-V and CHERI-MIPS engineering process. Those in the central column are all automatically generated from the Sail (and previously L3) formal ISA specifications. The CHERI hardware design is tested against the generated emulators, using both auto-generated and manually written tests (not shown). The CHERI software stack, including adaptions of Clang and FreeBSD, is developed by running above the generated emulators, the hardware, and a QEMU emulator (not shown). The security properties are stated and proved in terms of the automatically generated Isabelle version of the ISA specification.

conforming hardware implementation (and the proof work did uncover such errors in earlier versions). However, we have not proved the correctness of the CHERI hardware implementations of these architectures (for Morello, that remains beyond the state of the art), or of the software stack above it (though the architecture ensures that considerably less software has to be trusted).

#### Morello

CHERI has been designed from the outset to be widely deployable, but because it involves changes to the fundamental architectural interface between hardware and software, elaborating and evaluating the approach has required a great deal of work up and down the stack: detailed hardware design, microachitecture, the architecture design itself, adaptations to the software stack including C/C++ compilers, linkers, debuggers, FreeBSD, and FreeRTOS, and formal semantics, verification, and test generation to ease conventional engineering and improve assurance. It was developed as an academic research project from 2010 onward, but necessarily given the above, a rather large one: with around 100 people involved in one way or another and around \$40 million total funding. All this has produced academically convincing results (reported in many publications) and open-source artifacts.

Achieving widespread adoption of any substantial new architectural feature is challenging, as it needs coordinated hardware and software change across the industry. On the plus side, there are very few architecture vendors, so if a feature becomes (say) part of the mainline Arm architecture and there is pull from major partners, then it will be implemented in all conforming Arm implementations and become ubiquitously available in devices. Around 2018, CHERI faced a chicken-and-egg situation: while the academic results were strong, achieving such adoption needs an industry-scale evaluation to demonstrate viability and enable that pull, and that needs a high-performance silicon processor implementation and software stack above it. But that is beyond what can be done academically and hard to justify as a purely commercial project. The 2019–24 UKRI DSbD challenge, evolved from a 2018 Expression of Interest to the UK Industrial Strategy Challenge Fund, resolves this chicken-and-egg difficulty with a combined public-sector and industry program in excess of \$200 million to build and evaluate such a demonstration platform and support research and development above it [8].

Arm, in a consortium with the University of Cambridge, University of Edinburgh, and Linaro, supported in part by DSbD, has designed and built Morello, a CHERI-enabled prototype architecture,

processor, SoC, development board, and software stacks, extending the Armv8.2-A architecture and the high-performance Neoverse N1 processor [9, 10]. The formal verification of the Morello architecture design, described in the last section, provides assurance that it does provide the intended security properties. The complete CHERI software stack, including compilers, OSs, and applications, have been ported to the architecture. The architecture, emulators, and software toolchains have been available since 2019, and boards have begun to ship to academic, industrial, and government research labs in early 2022. DSbD is also funding further research and evaluation projects centered around Morello. All this will allow evaluation of CHERI mechanisms in a variety of configurations and use cases on a state-of-the-art hardware platform, and paves the way for the potential adoption of CHERI into future production architectures and devices.

#### CHERI capabilities on Morello

CHERI capabilities are twice the natural address size of the architecture plus an out-of-band tag bit, which is not independently addressable; for Morello, capabilities are 128+1 bits. As shown below, the lower 64 bits are the "value," which in most cases represents a virtual address. The upper 64 bits encode metadata, including bounds, permissions, and other mechanisms. The tag provides integrity protection: it is preserved only by legitimate operations on capabilities, and cleared by others. A capability can only be used as such (e.g., for a dereference if its tag is set).

| perms[17:2] | е | g | otype[14:0] | bounds[86:56] |  |  |  |  |

|-------------|---|---|-------------|---------------|--|--|--|--|

| value[63:0] |   |   |             |               |  |  |  |  |

A sophisticated compression scheme allows a capability to include 64-bit lower and upper virtual-address bounds [10, 19]. Small regions can be described precisely, with an arbitrary size in bytes, while for larger regions, only certain bounds and sizes are expressible. The capability value must be either within the bounds or within a certain range above or below, allowing for common C idioms that transiently construct (but do not dereference) slightly out-of-bounds pointers; other combinations of value and bounds are not representable. This scheme trades off bounds precision for reduced capability size; supporting arbitrary bounds would require more than 128+1

bits per capability, which would have unacceptable performance costs.

Four of the 18 permission bits are reserved for software, while the others have architecturally defined meaning. The Load, Store, and Execute permissions control whether a capability can be used for loading or storing data or fetching instructions. Permissions to control loading and storing of capabilities, as opposed to data, are also available. The System permission controls access to system registers and operations, in addition to the access control mechanisms of the base Arm architecture. Capabilities can also be sealed, making them immutable and unusable for anything but branching to them; this allows controlled transitions between different security domains. Sealing (or unsealing) a capability requires an authority capability with the Seal (or Unseal) permission; more on this in the next section.

#### Capabilities in registers and memory

Morello extends the Armv8-A general-purpose integer register file, as well as certain control and status registers, from 64 bits to 128+1 bits. Memory is extended with a tag bit for each 128-bit sized and aligned unit of DRAM.

The program counter (PC) is extended to become a *program-counter capability* (PCC), constraining instruction fetch as well as PC-relative loads (e.g., of global variables). A new DDC special register controls and transforms memory accesses relative to machine-word pointer values by legacy (non-capability) instructions, for legacy code using integer pointers.

#### Capability-aware instructions

Morello extends Armv8-A with new instructions and modifies existing instructions to use and respect capabilities. For example, a Load capability (literal) instruction LDR <Ct>,<label> calculates an address from the PCC value and an immediate offset, loads a capability from memory, and writes it to capability register Ct [10]. If the PCC capability does not have the load permission, or the calculated address is outside its bounds, a capability fault exception is raised. The tag of the PCC capability is also checked (already as part of instruction fetching). Most other instructions authorize loads and stores via a capability in an explicitly identified register, or use DDC, rather than implicitly use PCC.

Conventional execution flow is also controlled by capabilities, with branch and branch-and-link-register instructions to capability destinations (or implicitly with respect to the PCC for legacy instructions). Here, too, the capability must have its tag set and the target virtual address must be within the bounds, and in this case, it must authorize execution.

Then there are instructions to access and manipulate the fields of a capability, including arithmetic on its virtual-address value field (corresponding to conventional pointer arithmetic), comparisons, and other operations to extract and manipulate its permissions and other data.

Due to opcode-space constraints, Morello introduces a new instruction-decoding mode that reuses existing integer-relative load/store/jump instructions for capability-relative access.

#### Domain transition

CHERI distinguishes between sealed and unsealed capabilities. An unsealed capability can be used directly (e.g., to load and store), but a sealed capability can only be used to request actions be taken by other software. This feature can be used in the context of protection domains or software compartments, in which whole subsystems are given access to a limited subset of memory.

Domain X may have no direct authority to domain Y, but may call into domain Y by *invoking* one or more sealed capabilities originally sealed by (or for) Y. The invocation will install unsealed versions of the invoked capabilities in registers. This always includes replacing the current PCC; thus, this performs a jump to a specific code entry point provided by domain Y. These domain transitions are non-monotonic and must be treated specially in our proof.

Variations on this sealing and invocation mechanism enable slightly different calling styles. When sealing capabilities, they can be labeled with an *object type*, if the authorizing capability has that object type in its bounds. The "branch to sealed capability pair" instruction invokes a given code capability and also an argument data capability, checking their object types match, providing object-style encapsulation. Three kinds of specialized *sentry* (*sealed entry*) capabilities may be used transparently by direct branch instructions, memory-indirect branch instructions, and memory-indirect branch-to-pair instructions, respectively.

# Exceptions and the memory management unit

In addition to compiler-facing instructions, system functionality such as virtual memory, cache management, and exception handling is also extended. Exception handling preserves extended capability register state, and there are new exception cause codes associated with CHERI failures such as bounds violations or untagged memory accesses. Because exception handling is able to restore reserved registers during exception-level transitions, it is also a form of domain transition, as reserved registers may contain capabilities not available to the executing code. The page-table format has been extended to add new permissions to, for example, limit loading and storing capabilities.

#### Conclusion

Work proceeds apace both to explore and evaluate the use of Morello and to investigate the application of the CHERI ideas in other contexts. For further upto-date details, please see the web pages for CHERI at <a href="https://www.cl.cam.ac.uk/research/security/ctsrd/cheri/">https://www.cl.cam.ac.uk/research/security/ctsrd/cheri/</a> (especially the "Introduction to CHERI" and "Architecture specification" documents there), for Morello at <a href="https://www.arm.com/architecture/cpu/morello">https://www.arm.com/architecture/cpu/morello</a>, and for Digital Security by Design at <a href="https://www.dsbd.tech/">https://www.dsbd.tech/</a>.

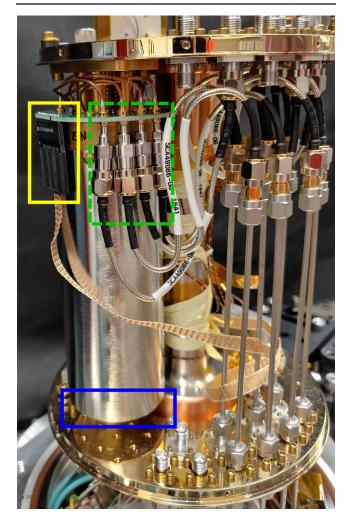

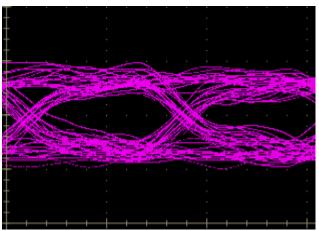

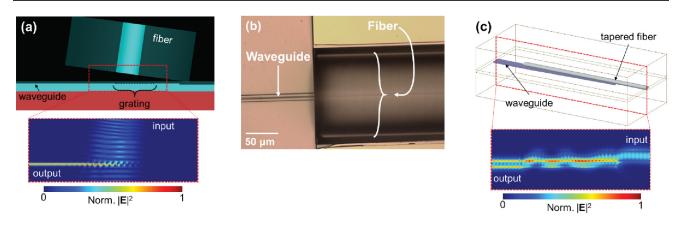

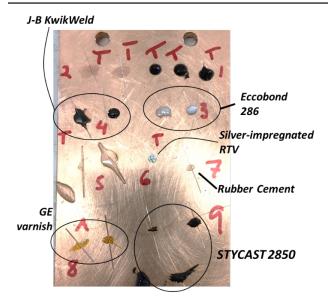

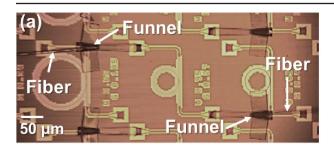

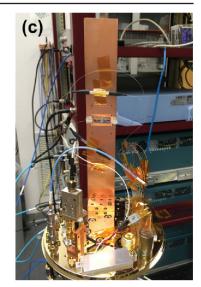

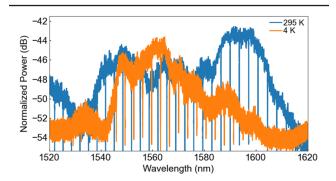

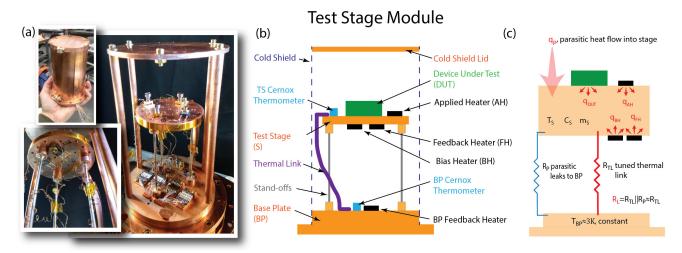

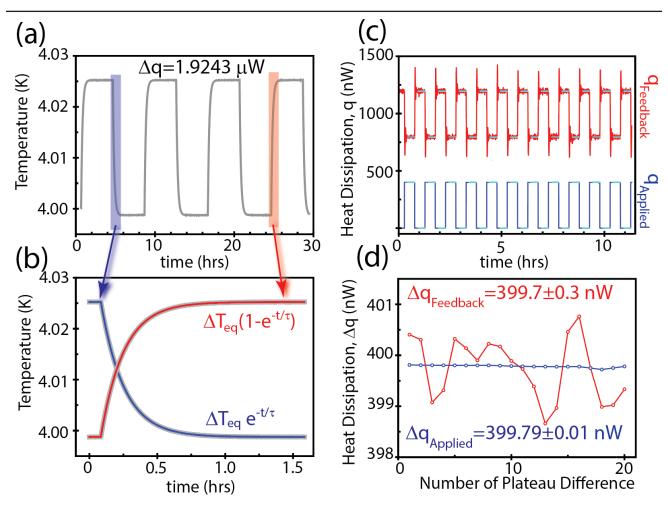

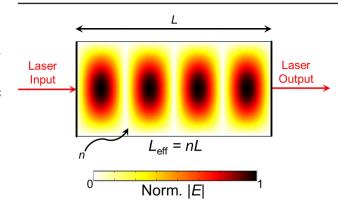

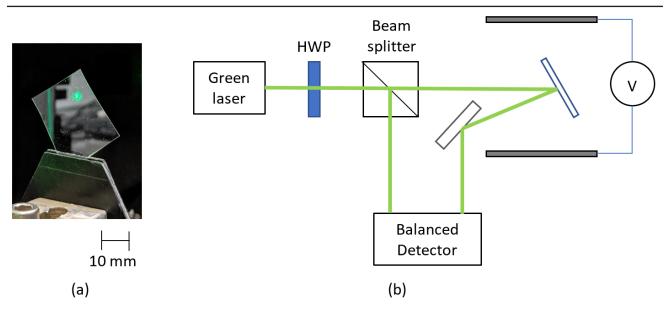

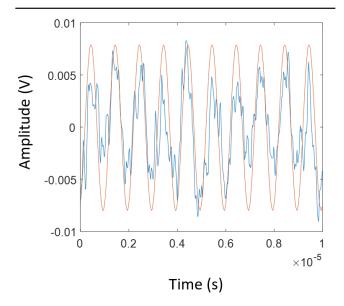

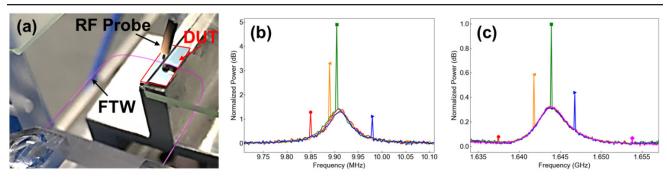

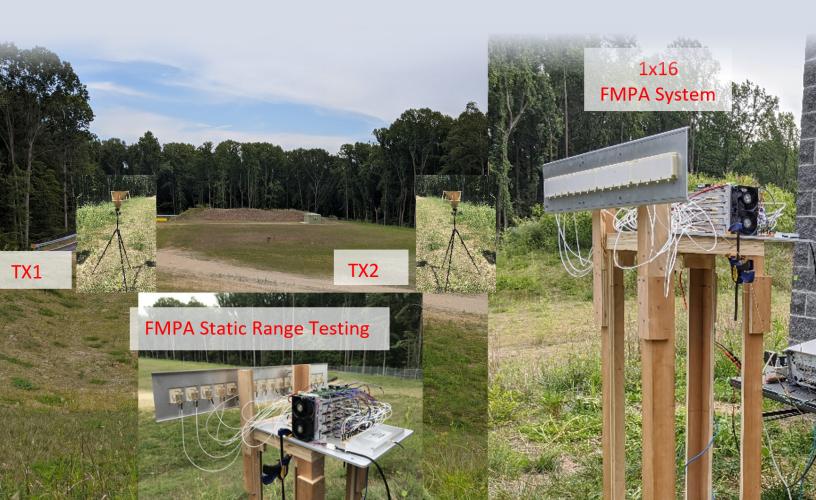

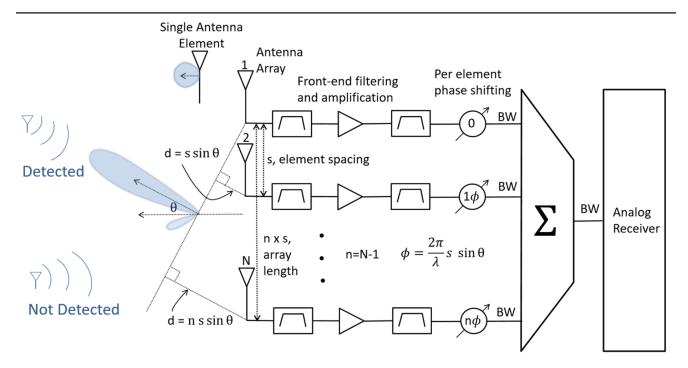

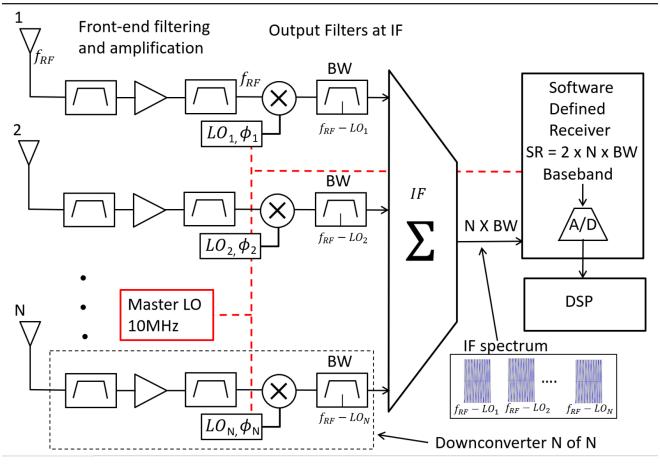

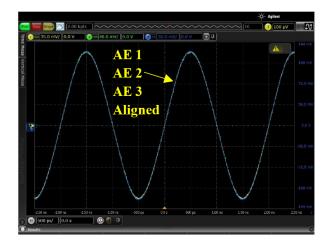

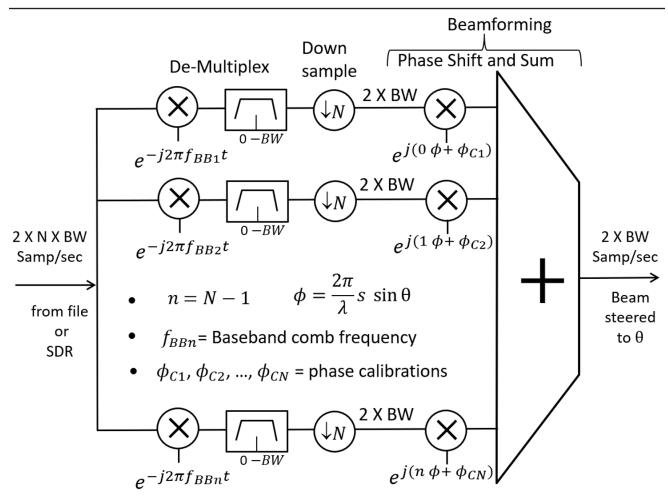

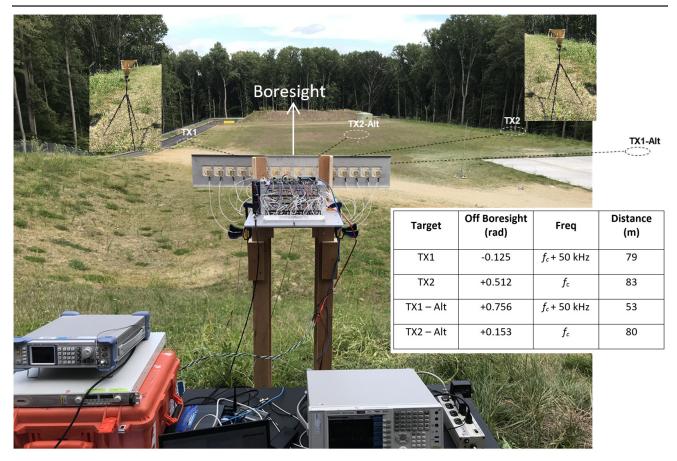

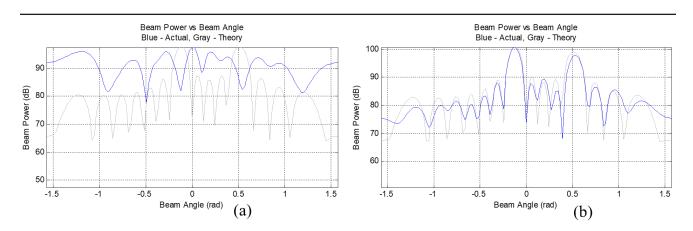

#### Acknowledgements